Една от основите цели, ако не и основната цел на закупуването на ATI Technologies от страна на AMD беше интегрирането на графичното ядро в централния процесор и навлизането в ерата на хетерогенните процесори. Всъщност компанията прокламира тази стратегия едва ли не от момента на сделката. При все това до съвсем скоро тя беше далеч от реализацията си. Нещо повече – изгубеното време позволи на Intel да изпревари AMD в тази насока като предложи интеграция на ниво пакет. Първите екземпляри на концепцията Fusion се появиха в края на миналата година под формата на свръхиконмичната платформа Brazos, която вече ви представих. Тя обаче си има своите ограничения в производителността, а всъщото време AMD започна драстично да изостава в средния клас спрямо Intel. В края на краищата след редица забавяния поради проблеми с производствените процеси и не само, ето че най-накрая компанията престави интегрирания си процесор и от среден клас.

Llano

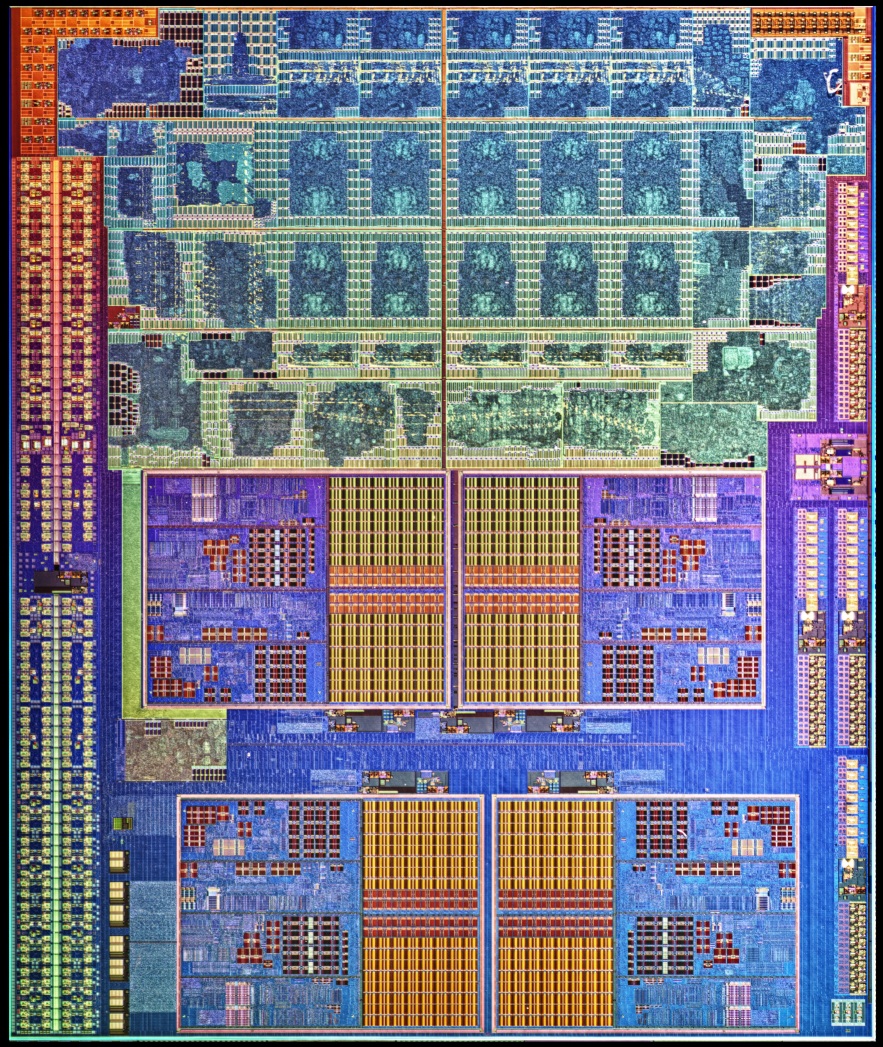

Llano (Ланоу) е кодовото име на новия процесор на AMD, който освен всичко друго е и първият модел произведен по 32 нанометров процес на компанията – „скромно” изоставане от около 1,5 години зад Intel. Отваряйки скоба – отделянето на производствените мощности компанията и намирането на мощен инвеститор освен всичко друго целеше и скъсяване на изоставането при въвеждане на новите производствени процеси спрямо Intel. Това обаче май не само не се случва, но и разликата се разширява, като преди беше около 1 година. Llano разчита на изпитани (което в компютрния свят се явява и в известен смисъл синоним на застаряващи) технологии от предишните поколения процесори и графични чипове на компанията, за да минимизира рисковете при производстовото, тъй като компанията вече веднъж се провали в опита си (така и непоявилата се архитектура Swift преди около 2,5 години). Процесорните ядра в чипасе базират на вече познатата K10.5 архитектура, използвана в популярните Athlon II и Phenom II процесори, а графичната част се базира на Redwood чипа използван в поколението 5ххх.

Не се е минало без някои леки усъвршенствания – процесорните ядра са леко подобрени, като са намалени латентностите на някои инструкции, разширен е инструкционния прозорец на блока за непоредно изпълнение от 72 на 84 инструкции, пипнати са и диспечерите, като целочислиния е разширен от 24 на 30 инструкции, а този на блока за плаваща запетая е увеличен до 42. L2 кеш паметта е 1 MB, както в двуядрените модели с ядро Regor, от Thuban-базираните X6 процесори Llano е наследил ТurboCore технологията, позволяваща динамично увеличаване на тактовата честота при натоварване само на част от ядрата. Сумарно подобрението би трябвало да достигне 6% повече инструкции на такт – не съвсем незабележимо, но крайно недостатъчно за конкуренция дори с предишната архитектура на Intel. AVX разширенията не се поддържат, като това остава сред предимствата на бъдещите модели от серията Buldozer и следващото поколение Fusion модели с кодово име Trinity. За да различаваме по лесно старите с новите ядра, то Llano ядрата ще наричаме K10.6.

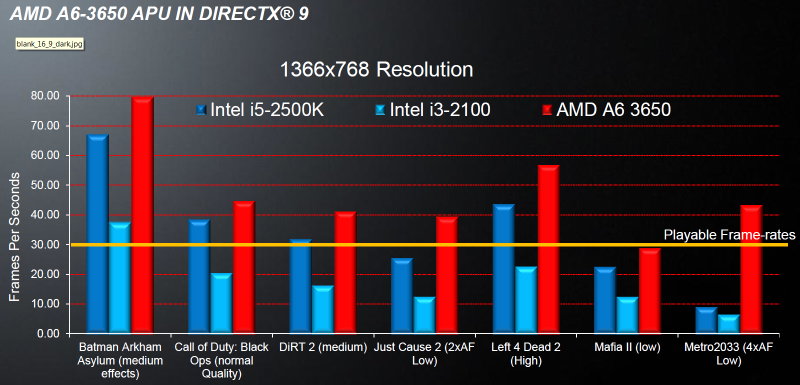

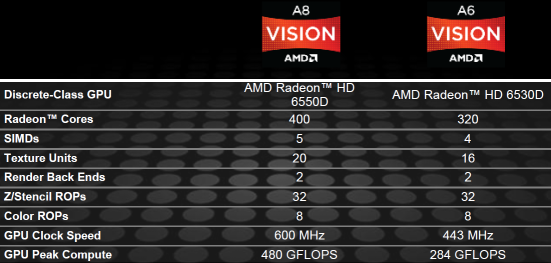

Графичното ядро, с кодовото име Sumo, на практика е целия Redwood (Radeon HD 5600/5500) вкаран в процесора, като при него борбата е била за прехвърлянето му от използвания при графичните чипове 40 нм процес на TSMC към 32 нм SOI технологията за производство на процесори на Global Foundries. Чисто архитектурно, графичната част е толкова подобна на Redwood, че връзката с контролера на паметта на процесора става през двуканална 128-битова шина (също както Redwood комуникира със събствената си памет), а комуникацията с процесора – чрез 16-битова шина (също като 16-битовата PCI Express шина за връзка на графичната карта), свързана към северния мост, вграден в чипа. По всичко изгледа, че единствената архитектурана разлика е премахването на физическите интерфейси на съответните шини. А това на свой ред означава наличието на цели 80 шейдерни процесора (400 АЛУ) групирани в 5 SIMD блока с общо 20 текстуриращи модула и два растерни блока с производителност общо 8 пиксела или 32 Z/stencil отчета на такт. И пълна поддръжка на DX11 включително Direct Compute и теселация, както и поддръжка на OpenCL. Впечатляваща спецификация за интегриран процесор, на практика на нивото на текущите модели от ниския среден клас. За съжаление обаче една от най-интересните за настолния пазар функционалности е премахната – Llano поддръжа 5 различни дисплейни интерфейса (DisplayPort, HDMI, DVI, LVDS, VGA), но само два от тях може да работят едновременно, което означава че не може да се организира Eyefinity конфигурация. За сметка на това UVD блока е променен и е във версия 3, което означава поддръжка на HD3D и хардуерно ускорено въпроизвеждане на Blu-Ray 3D. Заедно с това се завръща технологията Hybrid Crossfire X, която сега се нарича AMD Dual Graphics и позволява съвместната работа на графичното ядро с Radeon HD 6500 или 6400 модели в зависимост от спецификацията.

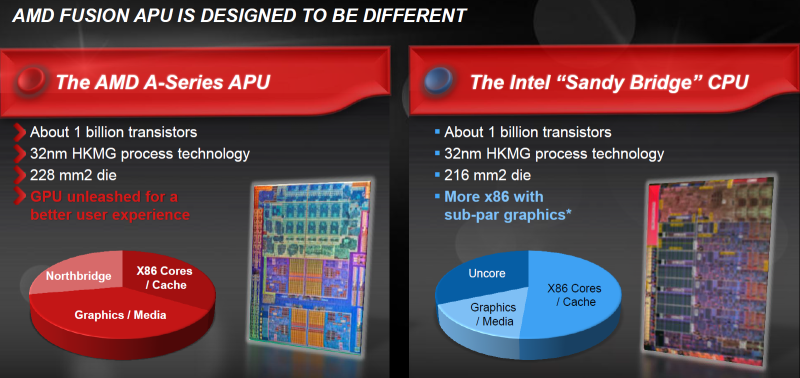

В добавка интеграцията при Llano вече включва и вграден PCI Express интефейс с общо 4 контролера по 8 линии, като става първия чип на компанията в този клас, реализиращ подобна степен на интеграция – северния мост на чипсета в пълна степен е вграден в процесора. Единия от контролерите се използва за реализация на дисплейните интерфейси, два от другите могат да се организират като един х16 или 2х8 PCI Express слота за поддръжка на CrossFire, а половината от линиите на последния контролер се използват за комуникация с Fusion Controller Hub или южният мост при традиционните чипсети, а останалите 4 могат да се конфигурират като 4х1 или 1х4 за допълнителни контролери. По същество изглежда нивото на архитектурана интеграция в Llano попада някъде между Arandale и Sandybridge, като процесорните ядра, графичния блок и северния мост на чипсета са интегрирани в един кристал, за разлика от двукристалния Arandale, но комуникацията между тях се извършва почти по същия начин, както ако бяха отделни чипове – основно през северния мост и RAM паметта. В същото време Sandybridge е дори по-напред в интеграцията, като графичното ядро може да използва L3 кеша на процесора както като локален буфер, компенсиращ недостига на пропускателна, така и за комуникация с процесор.

Интегрирането на графиката „зад” контролера на паметта е принудило компанията да отдели известно време за редизайн на този блок. Вкрани са сериозни оптимизации за подобряване на производителността, като контролерът вече следи и приоретизира различните заявки към паметта. Не е ясно точно как работи алгоритъма, но по всяка вероятност във всяка ситуация, в която е натоварен графичния блок, за него се заделя доста по-сериозна част от пропускателната способност, тъй като K10.6, като базирани на вече крайно остаряващата архитектура K8 не са особено лакоми за пропускателна способност. Заедно с това контролерът вече поддържа JEDEC спецификацирани DDR3 памети с тактова честота до 933 МХц (1866 МТ/с), като ограниченията са да се използват само по 2 модула и паметите да отговарят на спецификацията (10-10-10-30 или 11-11-11-33 тайминтги) с напрежение 1,5 В. Практически компанията не поддръжа различните по-стари овърклокърски варианти, макар че не това не означава, че обезателно няма да работят.

Сериозно внимание е отделено и на енергоспестяващите технологии. В Llano се използват активно clock gating (спиране на тактовия сигнал към даден блок) и power gating (изключване на подаването на захраването към даден блок). Благодарение на това неизползваните блокове на чипа се изключват, а когато цели ядра не работят, те не консумират никаква енергия. Същото важи и за графичното ядро. Clock gating не е нещо непознато при процесорите на AMD, но power gating е новост. В добавка L2 кеш паметта използва 8Т клетки, които са доста по енергийно ефективни, а не популярните 6Т клетки, които заемат по-малка площ. Подобно решение използва и Intel при процесорите си от Atom насам. Тези подобрения би трябвало значително да подобрят консумацията на процесора в ненатоварен режим и при сравнително слабо натоварване, ситуция в която всъщност те се намират през по-голяма част от времето.