Когато преди малко повече от година ви представих графичната архитектура Cayman на AMD писах, че на нея лежи бъдещето на компанията. Оказа се обаче, че не съм прав и през средата на миналата година, по времето на Fusion Developer Forum, AMD представи детайли от истинската си бъдеща архитектура – Graphics Core Next. А малко преди края на 2011-та година се появи и първият графичен чип базирана на нея, известен досега с кодовото име Tahiti.

Graphics Core Next

Архитектурите на AMD от R600 насам бяха базирани в общи линии на една и съща основа, като чиповете бяха разработвани преди всичко с идеята за графична производителност, макар че всяко поколение добавяше нови и нови възможности за работа като изчислителен процесор с по-общо предназначение. GCN архитектурата променя това – при нея GPGPU насочеността е много по-силна в сравнение с предходните поколения, като това е довело до наистина цялостна промяна. В известен смисъл от гледна точка на общите изчисления GCN e за AMD това, което беше Fermi за Nvidia, и дори повече.

Поколенията от R600 нататък бяха базирани на VLIW (very long instruction word – много дълга инструкционна дума) шейдерни процесори, които представляваха суперскаларни единици групиращи 5 (или 4 в случая на Cayman) АЛУ, можещи да работят едновременно върху различни инструкции в рамките на инструкционната „дума“. Всеки от изчислителните клъстери разполагаше с по 16 такива процесора, които могат да изпълняват едновременно инструкциите върху различни данни, т.е. типична SIMD архитектура. Това решение беше наложено при преминаването към унифицирана шейдерна архитектура, поради факта че доста добре работи за 3D графиката. По същество всеки такъв шейдер много наподобява по-ранните вертексни шейдери и запазва много висока ефективност за работа както с пикселните, така и с вертексните шейдери. В същото време обаче при по-общите изчисления е доста трудно да се използват всички АЛУ, а и за компилатора е сложно да оптимизира изпълнението на програмата, тъй като трябва да намести колкото се може повече независими инструкции в рамките на една дума.

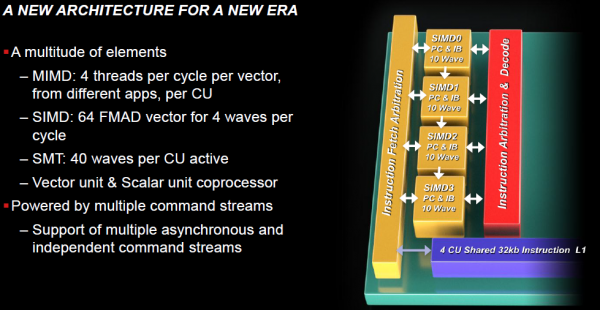

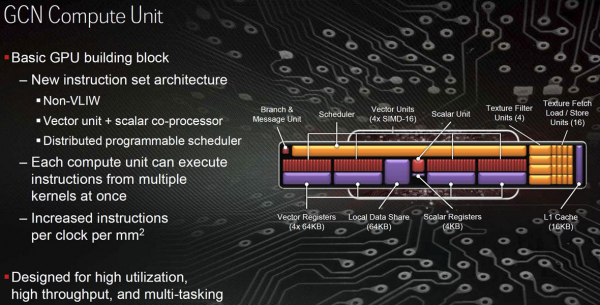

GCN се отказва от VLIW, макар да запазва същия брой АЛУ както при Кайман в рамките на един шейдерен блок. Вместо 16 VLIW блока, новата архитектура исползва само 4 отделни блока, но всеки от тях е векторен процесор съставен от 16 елемента. В известен смисъл това е като завъртане на 90о – вместо 16х4, сега конфигурацията е 4х16. Всеки от векторните процесори може да изпълнява по една инструкция на такт, но върху 16 различни елемента данни. По този начин значително се опростява работата на компилатора и програмиста, тъй като не се налага да се организира кода така, че да има максимален брой независими инструкции, които да се изпълняват едновременно. Сега изпълнението на програмата може да се сериализира инструкция по инструкцията, като за сметка на това трябва да се намерят достатъчно данни, върху които да се изпълни едновременно инструкцията. Това обаче е по-лесна задача при паралелните изчисления, за които обикновено се правят този тип процесори.

Тези промени опростяват диспечерирането на изпълнението на програмите в чипа. За сметка на това обаче се налага да се увеличи броят на поддържаните едновременно и изпълнявани нишки. В терминологиятa на AMD нишка е един фрагмент от данни, които се обработва, в случая на графичните изчисления това означава един от цветовите компоненти на пиксел. 64 фрагмента образуват един „уейвфронт“ (wavefront), което за графичните изчисления на практика означава 16 пиксела с по 4 компоненти (червена, зелена, синя и прозрачност). При VLIW архитектурите всеки SIMD клъстер се опитва да вземе колкото се може повече разлчини инструкции от един уейвфронт, за да ги изпълни едновременно. При графичните изчисления това е лесно, тъй като 4-те компонента на пиксела могат да се подадат на всяко от простите АЛУ-та на шейдерния процесор, като така целия блок от 16 пиксела може да се изчисли за един такт. При GCN обаче компонените се изпълняват последователно върху един векторен процесор, а всеки процесор изпълнява отделен уейвфронт, като се избира от общо 40 за изчислителен блок. Така за 4 такта и в двата случая ще имате изпълнени 4 уейвфронта. Всичко това е много хубаво, но извън графичните изчисления, твърде често не могат да се намерят 4 независими инструкции за едновременно изпълнение, като според данни на AMD средната използваемост на VLIW5 е едва 3,2 от 5 инструкции на такт, или малко над 60%. При Кайман използваемостта е по-добра, най-вече поради липсата на 5-тия модул и изпълнението на специалните операции върху 3 от простите АЛУ. При GCN използваемостта трябва да е още по-висока и да се доближи до 100%.

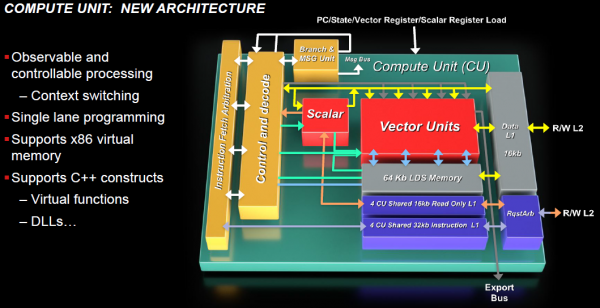

Това обаче не е всичко – за първи път в изчислителния блок (предвид промяната на означенията от AMD вече говорят за изчислителен блок – compute unit, вместо за SIMD клъстер, тъй като всеки от векторните процесори по същество е SIMD клъстер само по себе си) се появява и още един, отделен, скаларен процесор. Той е изцяло целочислен и поради това не се добавя към общите изчислителни възможности на чипа. Въпреки това скаларният АЛУ е от изключителна важност за новата архитектура, тъй като се занимава с управление на потока, генерация на адресите за указателите, както и за обработката на грешките. Благодарение на него новата архитектура може да поддържа всички възможности на езиците за програмиране като C++ (указатели, виртуални функции, грешки и други структури), нещо което не беше възможно при предишните поколения на AMD, но се появи като възможност във Fermi на NVidia. В този смисъл, един изчислителен блок вече може да се разглежда като пълноценно процесорно ядро, със целочислен конвейер и 4 векторни копроцесора и това е много сериозна стъпка напред. На практика всеки централен процесор в наши дни е комбинация между един или повече целочислени АЛУ и един или повече копроцесора за работа с плаваща запетая.

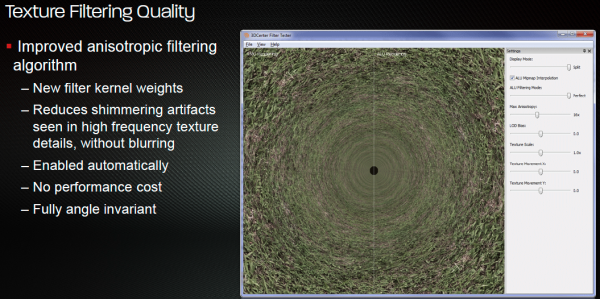

За разлика от VLIW5 и подобно на VLIW4, GCN не разполага с отделни блокове за специални операци, а те се изпълняват от векторните процесори със скорост 4 на такт (1/4 от максмалната производителост). Заедно с това векторните процесори могат да изпълняват FMA инструкциите както с единична точност, така и с двойна точност, като във втория случай производителността отново е 1/4 от тази с единична точност, също както при предишните поколения. От AMD обаче заявяват, че това съотношение може да се конфигурира между 1/2 и 1/16. Може би това означава, че този път ще видим поддръжка на работа с двойна точност и при младшите модели на фамилията. Заедно с това всеки изчислителен блок, разполага с блок от 16 модула за зареждане/запис и 4 модула за филтрация на текстури, т.е. 4 текстуриращи блока, които могат да се използват и за зареждане на данни за изчисленията. Няма данни възможностите им да са съществено променени, като отново FP16 форматите се обработват за 2, а FP32 форматите за 4 такта, но са направени някои промени в алгоритъма за анизотропна филтрация, които би трябвало да доведат до още по-добро качество и да намалят високочестотния шум, като се запазва ъгловонезависимия характер на алгоритъма.