Сагата с новата архитектура на Nvidiа на пръв поглед приключи през Април. Тогава най-накрая станаха достъпни комерсиално графичните адаптери GeForce GTX480 и 470, които се базираха на първия представител на фамилията Fermi – GF100. Пазарът на графични адаптери от най-висок клас обаче е силно ограничен, затова за масовото навлизане на DX11 съвместимите си адаптери, фирмата се нуждае от графични чипове от по-нисък клас. Първият опит беше GeForce GTX465, базиран на силно орязан вариант на GF100, с едва 11 работещи шейдерни мултипроцесора и 4 от 6 растеризиращи блока. Това вдигна добивите от GF100, но представения модел беше доста неконкурентен, а и използването на огромен чип от високия клас за навлизане на по-ниските нива на пазара не е особено смислено икономическо решение. И ето че през Юли се появи и първият дериват на Fermi, насочен към по-масовите модели. При това не просто дериват – GF104, както е кодовото название на чипа, е сериозен редизайн на архитектурата.

Промените

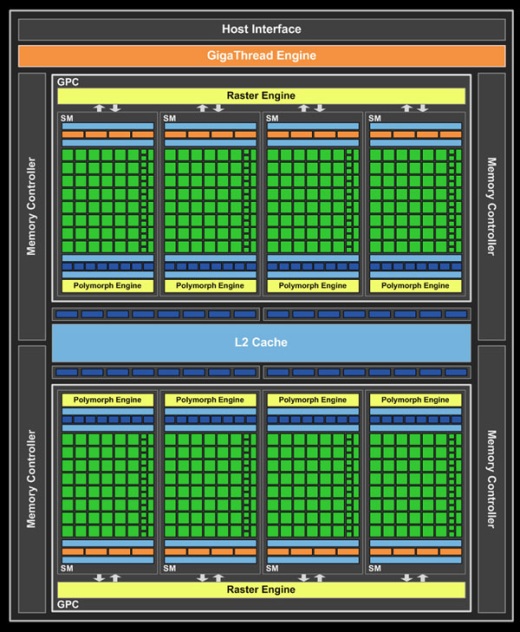

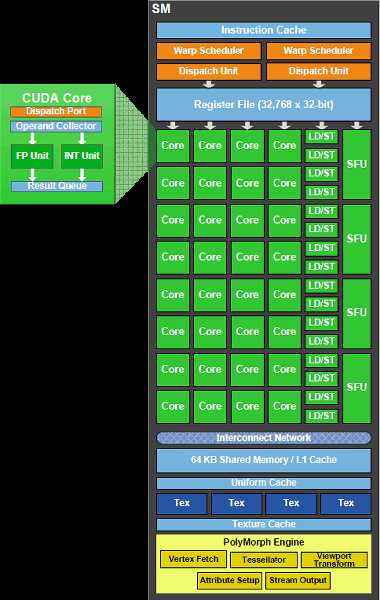

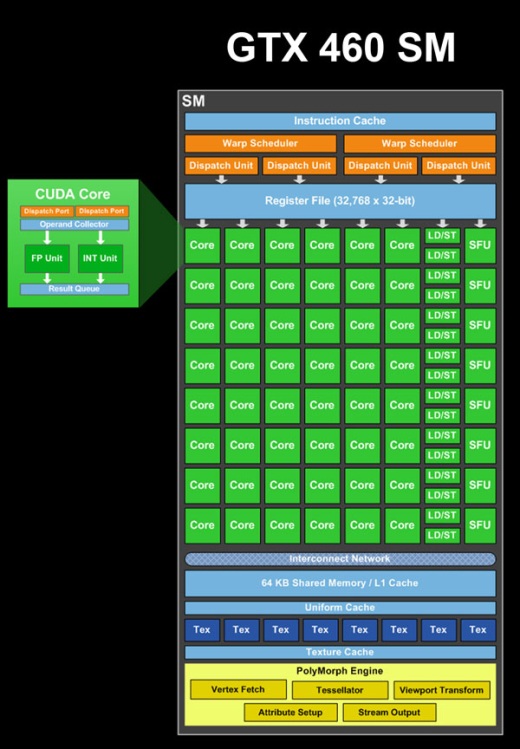

Обикновено, когато става дума за по-ниския клас сме свикнали NVidia да предлага деривати на топ чиповете си, които досега се различаваха най-вече по броя функционални модули. Смея да кажа че GF104 е вероятно първият случай, в който се появява не просто дериват, а сериозно променен и оптимизиран представител на архитектурата. В най-общ план нещата са запазени, новият графичен чип използва същата разпределена архтектура за геометрична обработка, като в случая са налични 2 графични клъстера, а не 4 както при GF100. Оттам нататък обаче започват промените. Всеки от клъстерите се състои от познатите ви 4 поточни мултипроцесора, но всеки от тях вече съдържа по 48 АЛУ, 8 текстуриращи модула 16 блока за зареждане/съхранение на данни и 8 модула за специални операции, срещу съответно 32/4/16/4 при GF100. Благодарение на това се запазват същия брой текстуриращи модули като във върховия модел, а изчислителните ресурси намаляват само с 1/4. Нещо което може би съм пропуснал при описанието на архитектурата Fermi в предната статия, е факта че все пак масива от 32 АЛУ в ПМ не е цялостен, а е разделен логически на две групи по 16 АЛУ. Така всеки от двата диспечера може да подава данни към 16 АЛУ, 16 ЗС блока, 4 МСО и 4 текстуриращи модула.

Оригиналния чип GF100...

Оригиналния чип GF100...В новата версия всеки диспечер може да разпознава независимите последователни инструкции и едновременно да подава до две инструкции на такт. В известен смисъл графичните процесори най-накрая стигнаха до идеята за суперскаларност. Така новата реализация може да изпълнява до 4 инструкции върху всяка от трите групи по 16 АЛУ, да задейства 16-те ЗС блока, да използва наличните вече 8 МСО или 8-те текстуриращи модула. По този начин GF104 теоретично би могъл да поддържа работещи 4 от 7-те си групи блокове, докато при GF100 могат да рабоятат едва 2 от 6 групи. Ако обаче диспечерите не могат да извлекат достатъчно инструкции, архитектурата може да се държи и като такава с 256 AЛУ, но все пак остават подобренията при текстуриращите модули и МСО.

Поточния мултипроцесор при GF100...

Поточния мултипроцесор при GF100... ... и при GF104.

... и при GF104.Друга промяна е физически намалените възможности за работа с данни с двойна точност, като такива е съхранил само един от трите АЛУ блока. Това означава че производителността на чипа при изчисленията с двойна точност е едва 1/6 от максималните изчислителни възможности срещу 1/2 при GF100. Това едва ли е голям проблем обаче, тъй като чипа и без това не е насочен към професионалния пазар, а и графичните версии на GF100 са софтуерно ограничени до 1/4 от максималната си ДТ производителност, за да не конкурират Quadro и Tesla продуктите. Някой би казал, че изобщо няма смисъл от ДТ изчисления при GF104, но от Nvidia имат доста силен аргумент, че това позволява на програмистите да разработват и тестват кода си и на по-евтини графични ускорители, което би улеснило процеса на разработка на софутер за професионалните модели.

Останалите промени са по-малки, като пропорционално е намален L2 кеша, който в новия чип е 512 КБ срещу 768 КБ в старшия модел. Nvidiа не го е заявила изрично, но според някои тестове е подобрена и производителността на текстуриращите модули в някои нестандартни режими с плаваща запетая. РОП блоковете са намалени от 6 на 4, което е довело и до намаляването на ширината на шината на паметта от 384 до 256 бита, но като функционални възможности не са променени. В същото време всеки PM може да обработва по два фрагмента на такт в архитектурата Fermi, което означава че и в този си вариант чипът е презапасен откъм растеризиращи възможности, като РОП блоковете могат да обработват до 32 пиксела/субпиксела на такт, а в същото време шейдерното ядро може да генерира не повече от 16 пиксела на такт. Това презапасяване ще е от полза при използване на AA, като например при 4х режим трябва да се обработват 4 пъти повече субпиксели.