Модул за обработка с плаваща запетая

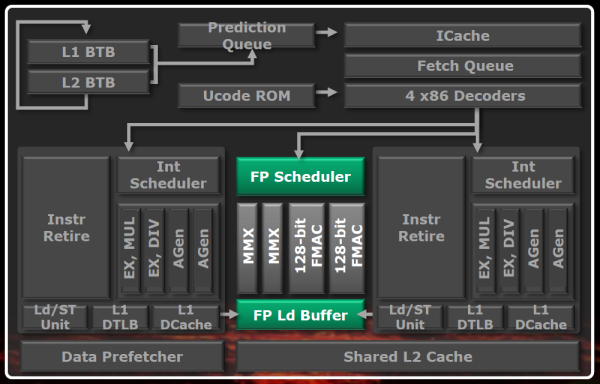

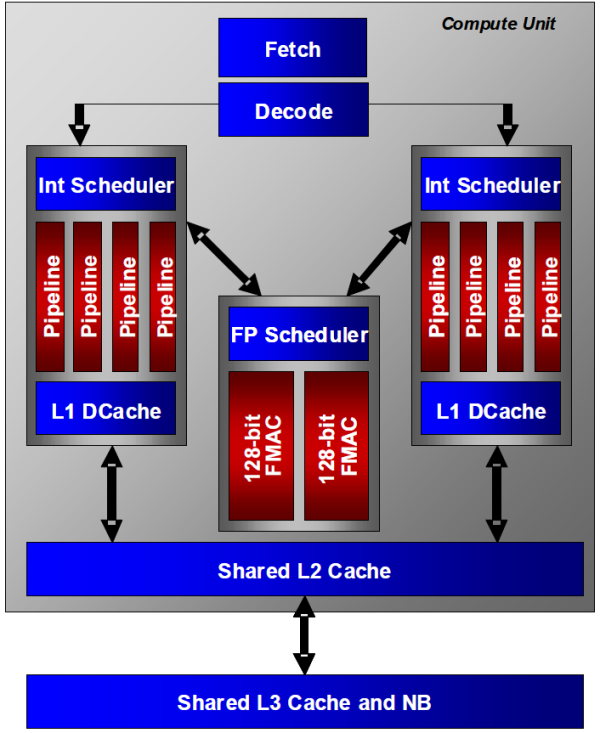

Копроцесорният клъстер също не прилича много на предшествениците си. Предишните две поколения на AMD рапзолагаха с общо 3 блока със ширина 128-бита, като два от тях се грижеха за реалните изчисления (един за събиране и един за умножение), докато третия реализираше деление и някои по-екзотични операции, както и се грижеше за работата с паметта. При Bulldozer нещата стоят много различно. Преди всичко той разполага с общо 4 блока, като два от тях се занимват само с целочислените векторни операции в MMX/SSE/AVX инструкциите. Другите два блока обаче са нещо което виждаме за първи път в настолен процесор – FMAC блокове. По същество това означава, че всеки от тях може да извършва както умножение, така и събиране, но заедно с това може с единична инструкция да реализира така нареченеото слято събиране-умножение (Fused Multiply-Accumulate, FMAC или FMA). Доскоро тази инструкция се използваше преди всичко при сигналните процесори и графичните адапери, но ето че вече, е на разположение и в нормалните процесори. Какво толкова и е специалното, все пак и в предишните процесори може да се изпълнява събиране-умножение (Multiply-Accumulate, MAC)? И в двата случая става дума за изпълнение на операция от типа a*b+c=d. Разликата е, че обикновената MAC инструкция всяка от двете операции се изпълнява отделно и се закръглява до текущата точност, което особено за умножението може да значи загуба на сериозно количество допълнителни битове. При FMA няма междинно закръгление и се работи с пълната точност на операциите, което означава че всъщност крайният резултат е с по-голяма точност от този на MAC. Нещо повече – при предишните поколения, за да се осъществи MAC, трябваше и двата изчислителни блока да работят заедно върху една инструкция. В Bulldozer това не е нужно, като всеки блок самостоятелно може да я зипълни, което реално удвоява пиковата производителност. Заедно с това фактът, че всеки от тях може да изпълнява както само умножение, така и само деление може да повиши ефективността в някои неравномерни откъм тип на операциите натоварвания. Заедно с това единият от двата целочислени векторни модула също може да изпълнява целочисления еквивалент на MAC.

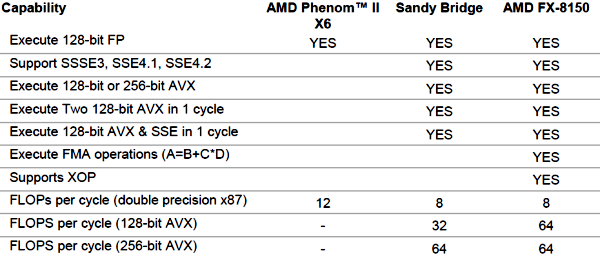

Тук обаче идва голямата уловка. FMA първоначално беше предвидена да се появи в 256-битовите векторни инструкции SSE5, представени от AMD. Това обаче не се хареса на Intel и те решиха да създадат собствен набор от разширени векторни инструкции, който вече ви е познат като AVX. За целите на съвместимостта от AMD се отказаха от собствения набор и преминаха към AVX, което често се сочи като една от причините за забавянето на Bulldozer. Проблемът обаче е, че AVX покрива само подмножество на SSE5 и една от областите, по които двете компании не могат да постигнат съгласие е FMA – докато AMD предложи използването на четериоперандна версия на инструкцията (по същество съхраняваща всеки от елементите на a*b+c=d), Intel предпочитат използването на триоперандната версия на инструкцията, при която крайният резултат се записва в един от трите входни регистъра. Макар че двете операции извършват едно и също дейстиве FMA4 е по-ефективна при големите изчислителни натоварвания, тъй като запазването и на 3-те операнда може да спести до 25% код в дадени случаи. В същото време FMA3 пък подлага на по-малко натоварване регистровия файл. Още по-лошото е че текущата версия на AVX, реализирана в процесорите SandyBridge на Intel изобщо не поддръжа FMA. Bulldozer обаче използва FMA4, но това означава че програмистите трябва специално да предвидят отделна версия на кода, ако искат да използват тази възможност. Освен разминавато с FMA, извън AVX остава още една група от инструкции, обединени под общото име XOP операции. Това по същество е целочислената версия на FMA, заедно с още няколко целочислени векторни операции и други. Те също са внедрени в Bulldozer и заедно с FMA имат много сериозен потенциал, който за съжаление не може да бъде разкрит без прекомпилиране на приложенията. Освен всичко останало, новите процесори напълно изравняват поддръжката на нови инструкции от страна на Intel, като се поддръжат всички версии на SSE до 4.2 включително, заедно с AVX и AES-NI. При това обаче от AMD прекратяват поддръжката на набора 3DNow!, който се появи за пръв път при моделите от фамилията K6. Това едва ли е учудващо, предвид факта че това са 64-битови операции и са почти напълно ирелевантни за съвременния софтуер, който използва преди всичко SSE2 и SSE3 за операции с плаваща запетая. Използването на 3DNow на практика би намалило производителността на съвременните процесори спрямо SSE2/3.

И накрая има още една особеност – копроцесорът няма собствени модули за зареждане и запис на данни, нито собствен кеш, единствено локален буфер за зареждане. При това той използват блоковете на целочислените ядра, предполагаемо в зависимост от изпълняваната в момента нишка. Заедно с това за изпълнението на 256-битовите AVX инструкции двата блока се сдвояват и работят както един общ блок. Това обаче означава че, за да използвате пълната мощност, трябва да използвате активирате едновременно и двата блока за зареждане/съхранение в двата клъстера, в противен случай може да е наложи да се изчака допълнително още един такт преди да може да започне изпълнението на следващата операция.