Кеш и памет

За завършек остава да кажем няколко думи и за архитектурата на паметта. За L1 кеш паметта вече стана дума. L2 кеш паметта е с обем 2 МБ на ядро, като е 16-кратно асоциативна, като поддържа опашка до 23 конкурентни пропуска за зареждане от паметта. И тук имаме сериозна промяна спрямо предходното поколение. До този момент архитектурите на AMD използват ексклузивна организация на паметта, като данните от по-горно ниво на памета не се копират в по-долното, като целта е максимално използване на обема. Радикалната промяна на рахитекурата в Bulldozer обаче води до промяна и в тази област. Ако се получи ситуация, в която данни нужни на единия поток се окажат в другия клъстер, то се налага те да се копират в локалнатата кеш памет. Това обаче е доста ресурсоемка операция. За това в новия процесор L2 кеш паметта се държи като инклузивна кеш памет спрямо L1 кеша, т.е. копира данните му в себе си, като по този начин се спестява част от комуникацията между клъстерите. Предвид огромната разлика в обемите загубата е минимална, а ползите явно превишават значително недостатъците. Заедно с това паметта използва протокол “write thru”, при който записът в кеш паметта се предава към следващото ниво в йерархията, а не по-популярния и ефективен вариант „write back“, при който данните се запазват локално само в кеша. “Write thru” увеличава натоварването на кеш паметта при запис, което още повече се усложнява от факта, че двата клъстера заедно могат да предизвикат презаписване. За това преди L2 в Bulldozer има малък по обем кеш, който служи за събиране и комбиниране на записите към L2 (Write Coalescing Cache, 4 KB), за да намалят натоварването. За съжаление и тук не е се е разминало увеличението на латентността, като тя вече достига до над 20 такта. Честно казано не е сигурно че четирикратно увеличеният обем би компенсирал в пълна степен увеличената латентност, още повече че сега кешът трябва да обслужва и две нишки. Връзката между L2 и ядрото изглежда остава същата както във Phenom – две отделни еднопосочни 128-битови шини.

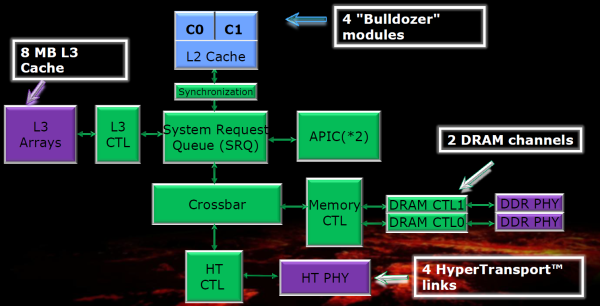

L3 кеш паметта остава отново отделно от ядрата, обвързана с честотата на северния мост и контролера на паметта, като в актуалните процесори варира между 2 и 2,2 ГХц. Тя е с обем 8 MB, като е разделена на 4 двумегабайтови блока, като е възможно отделянето на един от тях за филтър на трафика (snoop filter) в многопроцесорни системи. За съжаление няма данни каква е шината към L3 кеш паметта, но по всичко изглежда, че или е съществено разширена, или всеки от 4-те блока ползва собствена 64-битова шина, като четирите са свързани в обща комутаторна среда с ядрата и се използва interleaving между отделните блокове. За това съдя по значително увеличената производителност при четене, която в новия чип е приблизително 2,5 пъти по-висока в сравнение със старите модели.

Контролерът на паметта също е преживял значителни изменения, като в много отношения е сходен с този в Lano. Запазва дувканалната му архитектура. Официално поддържаната памет е до DDR3-1866 включително, но са налични множители и за DDR3-2000/2133/2400. Вътрешната производителност на контролера също е повишена, като са е внедрени алгоритъми за приоритеизация на заявките. Максималния брой слотове остава по два на канал. Всички тези добавки би трябвало да доведат до сумарно 50% повишение на производителността при операции с паметта спрямо преходното поколение. Максималната пропускателна способност достига до 29 ГБ/с, като тепърва предстои да видим колко от нея е реално използваема от процесора. При все това тази двуканална система предлага теоретично по-висока производителност спрямо триканалната памета на топмоделите от поколението Nehalem на Intel.

И накрая – процесорът запазва 4-те HyperTransport шини за връзка с чипсета и с другите процесори, ако се използва за създаването на сървърните процесори Opteron. Новото при тях е използването на версия 3.1 на протокола, която позволява максимална скорост на трансфер от 6,4 GT/s, но отново това ще е достъпно само във сървърната версия на процесора. При декстоп моделите, честотата е ограничена до 5,2 GT/s, като се използва само една от линиите. Ширината е запазена, като отново се използват две еднопосочни 16-битови шини, което дава пикова 25,6 ГБ/с на шина при сървърната версия или общо над 100 ГБ/с ако се използват и 4-те.