Cayman

Cayman в цялата му прелест.

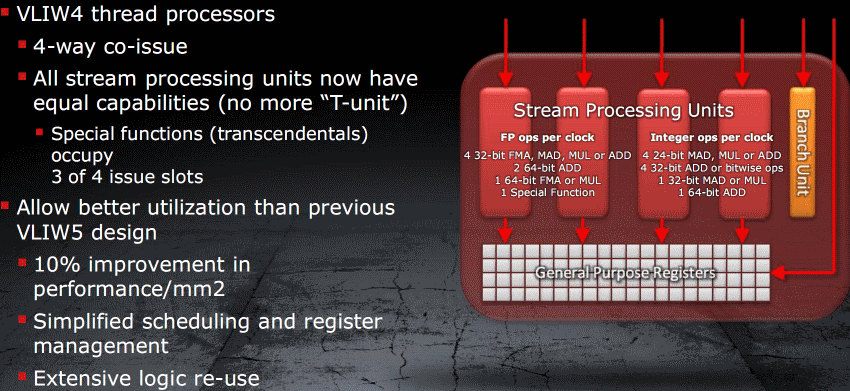

Cayman в цялата му прелест.Докато Barts е последната и най-ефективна инкарнация на познатата още от времето на Radeon HD 2900 VLIW5 архитектура на ATI, то Cayman е първата изцяло нова архитектурата на компанията откакто попадна под шапката на AMD. И тя дебютира отново във високия клас, където всъщност е и най-важна. Предвид страхотните резултатите постигнати от Barts може да се запитате защо е било нужно на AMD да сменя архитектурата? Най-важната причина може би GPGPU поддръжката. NVidia направи гигантска стъпка напред в програмируемостта на графичните си процесори с Fermi, като на пръв поглед изглеждаше сякаш са пожертвали в някаква степен игровата производителност. AMD в същото време изостават в известна степен на изчислителния фронт, а и при тях промените в тази насока винаги са били доста по-плавни. Защо обаче е нужна промяната на архитектурата? Старата VLIW5 архитектура води началото си още от ранните години на DirectX 9, при което ATI са избрали тази структура за вертексните шейдери като най-оптимална с възможност на един такт да се обработят както координатите на един връх, така и компонентите на осветеността. Това наследство от вертексните шейдери е пренесено и при първата унифицирана архитектура, тъй като тогава не са били готови да жертвата добрата геометрична производителност. VLIW5 обаче не е симетрична архитектурата като 4 от блоковете са сравнително прости, съсредоточени основно в работата с MADD/FMA инструкции за максимална изчислителна производителност, те също изпълняват и 64-битовите инструкции. По-големият т.нар. „дебел“ или „T“ модул пък може да изпълнява повече целочислени и специални операции. Това води до проблеми при планирането на операциите, за да може да се извърши осъществи оптимално натоварване на всички модули на чипа, което се усеща може би най-вече в GPGPU приложенията. Заедно с това значението на трансцеденталните и други подобни по-сложни операции намалява. И накрая, но вероятно съвсем не на последно място, вътрешните тестове на компанията показват че средното ниво на използване на 5-те АЛУ на всеки шейдер е едва 3,4, тоест едно от аритметико-логическите устройства на практика само заема място без да върши работа. Така че от AMD решават да го „изпратят в пенсия“ и така се появява новата VLIW4 архитектура, при която функционалността на „дебелия“ АЛУ се пренася равномерно в останалите блокове. Cayman е първият й представител.

Премахването на един от логическите блокове на шейдера обаче има и своите недостатъци. Сега, за изпълнението на една специална операция, диспечера заема 3 от слотовете във всяка инструкционна дума, което води до по-ниска производителност в този случай. Представете си следния случай – дълъг пикселен шейдер, който има 50 инструкции, 38 от които са MADD, 10 са трансцедентални и 2 за текстурни. При това положение при старата архитектурата те теоретично биха могли да бъдат комбинирани в 10 инструкционни думи. При новата архитектура обаче биха били нужни цели 17 такива. Разбра се това е много краен пример, както сочи 3,4-те слота средно запълване според AMD, но и означава че е възможно да има ситуации в които новите процесори се справят забележимо по-бавно от старите. Това на теория би трябвало да се компенсира от увеличения брой изпълнителни устройства, като според компанията при новата архитектура един SIMD клъстер заема с 10% по-малко място. В същото време работата през последните 4-5 години е оптимизирала шейдерния компилатор в драйверите именно за VLIW5 архитектура, тъй че е напълно възможно драйверите още доста време да се оптимизират под новата архитектура.

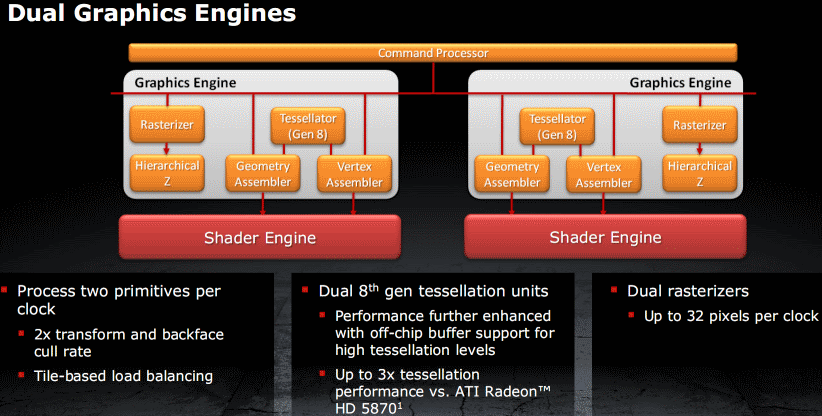

Двата сетъп енджина са комбинирани и с двойка теселатори за сериозен скок в производителността при теселация.

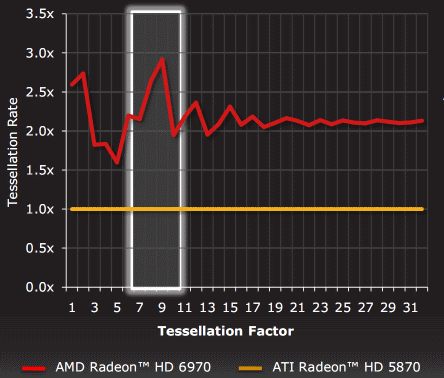

Двата сетъп енджина са комбинирани и с двойка теселатори за сериозен скок в производителността при теселация.VLIW4 обаче далеч не е единственото нововъведение в чипа. Втората изключително важна промяна е добавянето на втори сетъп енджин. Така вече и AMD имат разпределена геометрична система, подобно на въведената от NVidia с Fermi. Те обаче са доста по-консервативни в това отношение, като могат да подават на графичния конвейер максимум 2 полигона на такт срещу 4 при Fermi. Тази стъпка е много важно нововъведение особено предвид усилващия се интерес към теселационните възможности на графичните чипове. Заявка че подобно нещо е възможно даде още Cypress, но при него реализацията на разпределения геометричен цикъл беше непълна. За да се захранят ефективно пък двата двигателя, новия чип използва тайлов механизъм за разпределение на натоварването, при което изображението се разделя на малки зони (тайлове) и данните от всяка зона се предават една след друга на двете ядра. Удвояването на сетъп енджините е комбинирано и с добавянето на втори теселатор в чипа и въвеждането на буфер с възможност за преливане на данните към паметта, за да може теселацията да не блокира целия графичен конвейер при препълване на опашката от примитиви, както това се случва при предишното поколение. Всичко това води до дори по-голямо подобрение спрямо Cypress в сравнение с Barts, което варира между 50% (при оптималния за Cypress фактор 5х) и 200% (фактор 9х), като дори при големи фактори остава около 100%.

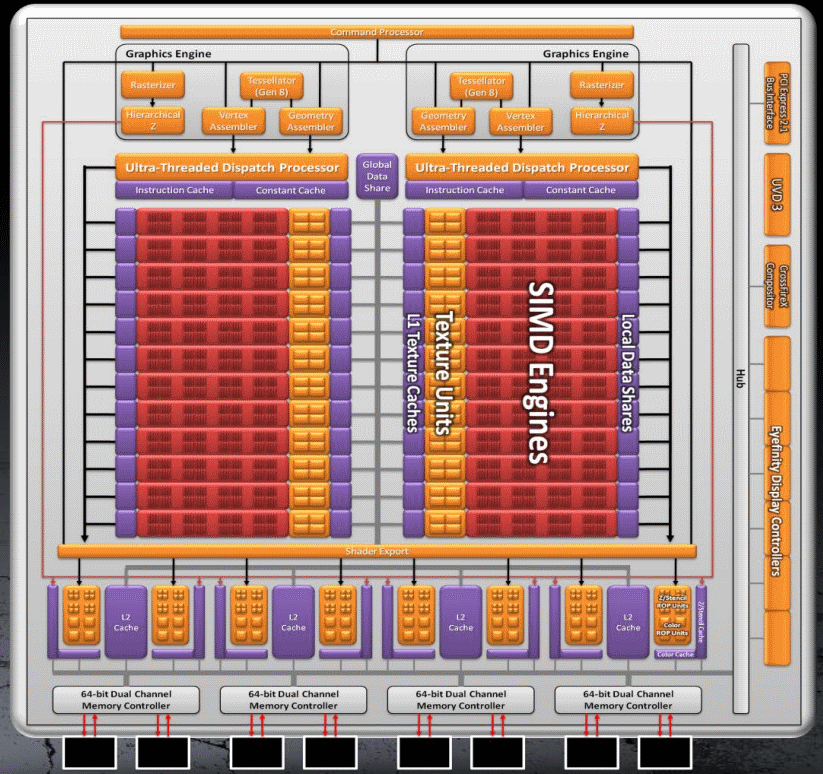

Използването на две геометрични машини вероятно ви е навело на мисълта, че в голяма степен основната структура на шейдерното ядро е запазена подобна на Cypress, а именно SIMD клъстерите са разпределени в два големи блока (Raster processing engine в терминологията на AMD, грубо преведено като Ядра за растерна обработка – ЯРО), като вече всеки от тях е захранван от собствен сетъп енджин, теселатор и растерен блок. ЯРО вече прилична на съвсем пълноцено процесорно ядро. Всеки от тези блокове разполага с масив от SIMD клъстери, като в този случай те са 12 или общо 24 за целия чип. Предвид новата архитектура това означава 1536 АЛУ/384 шейдера и 96 текстуриращи модула, или малко по-малко АЛУ спрямо Cypress, но групирани в повече шейдери и с повече текстуриращи блокове. При все това предвид по-добрата използваемост на модулите това означава че ефективните стойности за Cayman са по-високи от тези за Cypress (3,4×384 срещу 3,4х320). Заедно с променената архитектура на шейдените процесори всеки от клъстерите е получил и подобренията на текстуриращите модули на Barts, което значи адекватна работа на анизотропната филтрация. Всеки от растеризаторите пък може да генерира и интерполира 16 фрагмента, което означава че тези 12 клъстера би трябвало да са добре захранени с данни. Заедно с това новата архитектура балансира напълно входа и изхода на чипа, като на входа на шейдерното ядро могат да се поставят до 32 фрагмента, които накрая да завършат изпълнението си като 32 пиксела през ROP блоковете на чипа.