Какво е Bulldozer?

Bulldozer е първият радикален нов процесорен дизайн на AMD от цели 12 години, когато се появи първият K7 базиран Athlon. Всички последващи процесори на компанията са базират малко или повече на развитие на концепцията K7. Нещо повече Bulldozer е и първата реализация на процесор с клъстерна многопоточa обработка за масовия пазар. Важно е да отбележим, че новият дизайн на AMD не е първият изобщо реализиращ подобен тип архитектура, но е първият при декстоп процесорите.

Да ви прилича на 8-ядрен процесор?

Да ви прилича на 8-ядрен процесор?Какво не е Bulldozer?

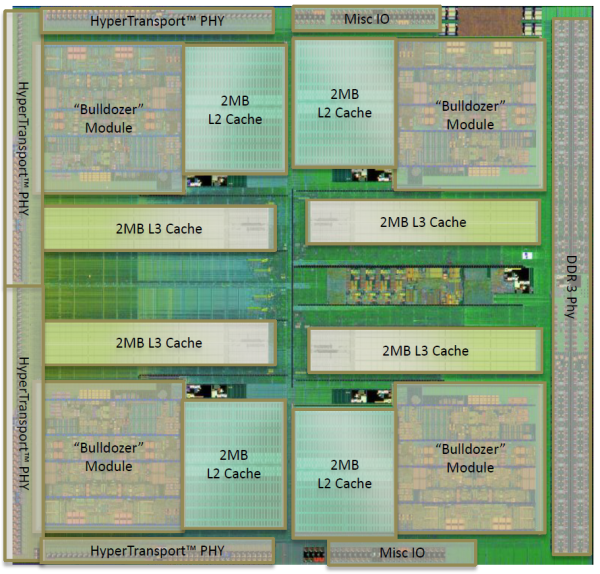

Въпреки рекламите, Bulldozer не е 8-ядрен процесор, както го представя маркетинга на AMD. Bulldozer е 4-ядрен, 8-клъстерен процесор, като всяко процесорно ядро разполага с два целочислени клъстера. Именно тях от AMD наричат “x86 ядра”, опитвайки се да размият концепцията за процесорно ядро, дефинирайки я като „всеки елемент можещ да изпълнява целочислени операции и разполагащ със собствена инструкционна опашка“. Още по-забавната част е, че това е “x86 ядро”, т.е. предполагаемо трябва да може да изпълнява х86 процесорни инструкции. Истината обаче е, че така наречените „ядра“ не могат да изпълняват х86 код сами. Това което изпълняват всъщност са вътрешни, AMD-специфични инструкции – микрооперации. Така че извадите ли т.нар. “ядро“ извън процесора, с него не може да правите почти нищо.

За това в тази статия ще използвам различна терминология от тази, с която ще ви захранват повечето останали сайтове, което, признавам, може да е объркващо. Т.нар. от AMD модули, всъщност са истинските процесорни ядра на чипа, а “x86 ядрата” са просто отделени целочислени клъстери – група целочислени конвейери, разполагащи със собствен диспечер. Ако текстът ви обърква, просто заменетe „ядра“ с „модули“, а „клъстери“ с „х86 ядра“.

Фронтендът

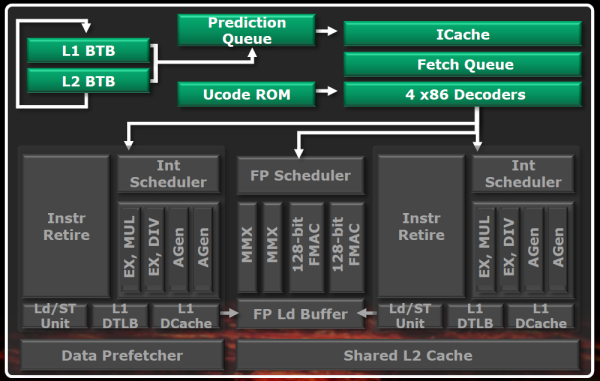

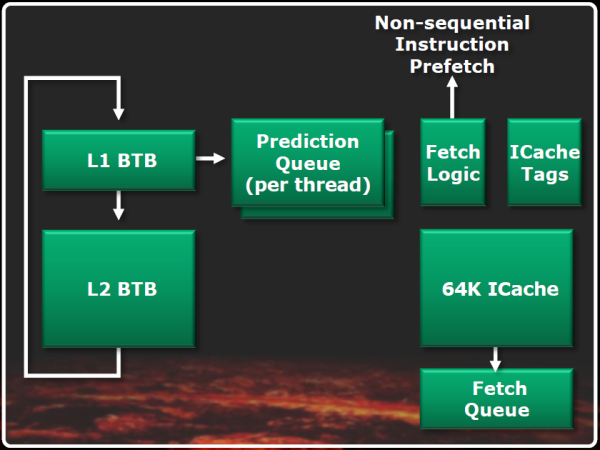

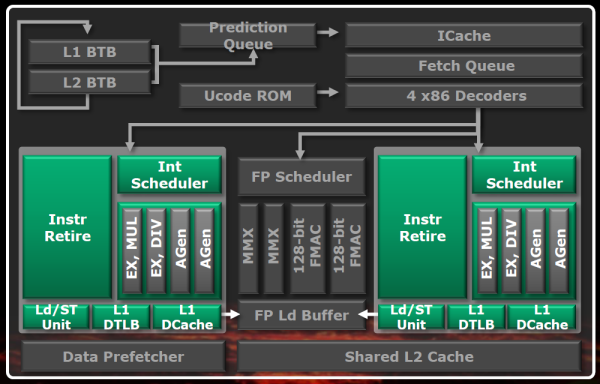

Това е началната точка на изпълнението на инструкциите в процесора. Фронтендът при х86 процесорите с състои от логиката за извличане на инструкции и предсказване на преходите, както и от декодерите на инструкции. Първата разлика с предишното поколение на компанията, Phenom II, e в разделянето на етапите на предказване на разклонеията и извличането на инструкции. В старата архитектура тези две дейности се извършват заедно, като евентуалната нужда от изчакване на извличането води до блокиране на предказването на разклонения. В Bulldozer тези два етапа са рааделени и предказването може да се осъществява паралелно с извиличането, като резултатте се натрупват в буфер. Конкретните параметри на блока не са разкрити от AMD, така че не е ясно колко ефективен е процеса. При все това предвид ориентацията на процесора се предполага ефективността да е много висока. След осъществяването на правилно предвиждане чипът трябва да изтегли информацията от паметта. За това му помага 64КБ инструционен кеш с двукратна асоциативност и 256 битова шина. Заедно с това чипът разполага с буфери, в които се пазят указатели от превидените разклонения (Branch Target Buffer). Размерът на тези буфери е 512 инструкции за L1 кеша паметта и 5120 за L2. Друга особеност е използването на буфер за транслиране на инструкциите (Translation Lookaside Buffer), който с две нива и има съответно 72 инструкции за L1 и 512 за L2 кеша. Ширината на буфера за избор на инструкции остава 32 байта както при Phenom, но броят на буферите е удвоен, за да поддържа двата потока. Всеки от буферите може да съдържа по 16 записа. Декодерите могат да взимат по един запис от който и да е от двата буфера, като така нишките се редуват през такт.

Самите декодери в новия дизайн са увеличени до 4, спрямо предишните 3. И четирите декодера са симетрични, като могат да декодират една х86 инструкция в една или две вътрешни макрооперации. Макрооперацията представлява пакет от една изчислителна инструкция и една операция с паметта или преход. По-голямата част от х86 инструкциите се декодират в една макрооперация, малка, но съществена част, се декодира в 2 макроперации, и много малка част се декодира в повече от 2 операции. За последните се грижи микрокод блок, който не е ясно с каква точно поризводителност е, но според изявлаениятa на компанията би трябвало да е поне толкова бърз, колкото този във Phenom, което предполага поне 3 инструкции на такт. Всичко това е прилично подобрение спрямо предходното поколение и най-накрая достига до нивата на процесорите на Intel, които декодират по 4 операции на такт от няколко поколения. Декодерите освен това са усъвършествени спрямо тези във Phenom и поддръжата „branch fusion“ или сливане на клоновете, което позволява да се групират различни операции за проверки и преходи заедно с изчислителни операции.

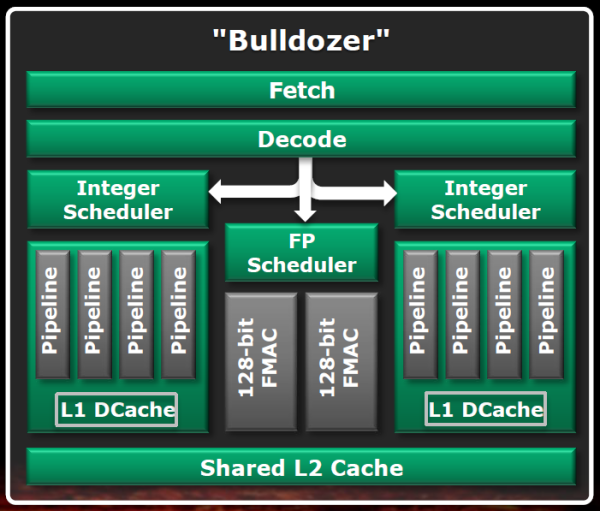

Целочислените блокове

Следващата стъпка е постъпването на макрооперациите в опашка за проследяване на изпълнението (Retirement Queue) с размер 128 записа, която служи за проследяване на пътя им в чипа и да ги разпредели към изчислителните блокове. И тука идва най-съществената особеност на Bulldozer – както вече казах той реализира клъстерна многопоточност. От AMD са избрали да дублират единствено целочислените ресури на чипа, тъй като това са типично преобладаващите операции в повечето приложения. По този начин всяка от нишките разполага със собствен целочислен клъстер, но двете споделят общия блок с плаваща запетая, който на практика работи като копроцесор на принципа на едновременната многопоточност. Всеки от целочислените клъстери разполага със собствен диспечер поддръжащ 40 макрооперации, а копроцесорът има също собствен диспечер за 60 макроперации, като може да получава самостоятелно съответните инструкции, но приключването им минава през целочислните клъстери, които единствено съдържат съотвените блокове за приключване на операциите (Instruction Retire Module). Инструкциите от отделните нишки се редуват през такт. Заедно с това целочислените клъстери разполагат с 96 регистъра, докато блока за плаваща запетая има 160. При влизането си в диспечера макрооперациите се разбиват на елементарните си микрооперации (изчислителна и адресна), които в последствие могат да се подават за непоредно изпълнение от изчислителните устройства. Важно е да се отбележи, че в Bulldozer се използват физически регистри, подобно на енергоефективната архитектура на AMD – Bobcat. Идеята зад това е данните да се пазят само на едно място и да се предват само указателите им, тъй като преместването на данните между регистрите е изключително енергоемка операция.

Всеки от целочислените клъстери разполага с по два АЛУ и два АГЛУ. Едно от АЛУ може да изпълнява и целочислено умножение, а другото – деление. По-интересния момент е, че двете адресо генериращи устройства са допълнени и с елементарно логическо устройство (отам и АГЛУ), като могат да изпълняват и някои прости операции. В този смисъл в определени ситуации целочисления клъстер може дa се държи като 4-конвейерен, а не като двуконвейерен. Заедно с това достъпите до паметта са напълно непоредни, стига да не са от взаимозависими инструкции. Подобна степен на независимост има при процесорите на Intel още от времето на Core 2, докато при Phenom възможностите са по-ограничени. Като заговорихме за предходното поколение, трябва да отбележим че всеки от клъстерите сам по себе си разполага с по-малко изчислителни ресурси в сравнение с едно К10 ядро, което съдържа 3 двойки АЛУ+АГУ. Според AMD третия комплект устройства е бил много рядко използван, за това премахването му нямало да се усети съществено. Честно казано не съм твърде уверен колко е вярно това, но по този начин целочисленият клъстер повече прилича на ядрото на енергоефективната архитектура Bobcat, която не блести с производителност, отколкото на съвременна високопроизводителна архитектура. Сумарно обаче едно Bulldozer ядро разпоалга с повече ресурси от едно Phenom ядро (4 АЛУ+ 4 АГЛУ), но за момента по всичко изглежда, че не е възможно целият ресурс да се използван от една нишка.

Всеки от целочислените клъстери разполага и със собствено устройство за зареждане/съхранение на данни, както и собствен 16 КБ кеш за данни със 4-кратна асоциативност. Устройството за съхранение на данни може да изпълнява едновременно 2 128-битови зареждания от паметта и по един 128-битов запис или общо 3 операции. В същото време всеки клъстер може да гененрира само по 2 два адреса на такт. Блокът разполага с опашки от 40 записа за зареждане и от 24 за съхранение на данни. В това отношение клъстерът не е много далеч от възможностите на K10, който може да осъществи едновременно 2 128 битови извличания и два 64-битови записа. За сметка на това L1 кешът при Bulldozer е 4 пъти по-малък, но с нарастнала асоциативност (от двукратна на 4-кратна). Докато подобрената асоциативност увеличава броя на попаденият в кеша, то размерът му ще намали съшествено данните, които могат да се съдържат в него. Заедно с това латентността на кеша е увеличена от 3 на 4 такта, като това е направено с цел постигане на по-високи честоти. Сумирайки всичко заедно по всичко изглежда, че производителността в еднонишковите приложения няма да е от силните страни на Bulldozer и има доста голяма вероятност новият модел не само да не може да настигне конкурентите от Intel, но дори да изостава зад предходното поколение на AMD.