В първата част ви представих вграденото видео в новата фамилия процесори на Intel, и е крайно време да демонстрирам и на какво е способна процесорната част. По принцип тя е по-малко интересната, тъй като е базирана на вече добре познатите Sandy Bridge ядра с минимални усъвършенствания, но тъй като и самите Sandy Bridge не са представяни на сайта, се пригответе за сериозно четене.

Архитектура

Ако се върнете към теоретичната част в представянето ми на Bulldozer архитектурата на AMD и погледнете отново нещата, то можем да опишем Ivy Bridge като съчетаващ SMT и CMP архитектурите като процесорът разполага с 4 процесорни ядра, всяко от които може да изпълнява по два потока едновременно. Така, подобно на Bulldozer, чипът може да работи с до 8 нишки едновременно, но при това положение споделя между тях доста по-голяма част от ресурсите си. “Уловката” обаче е, че отделното процесорно ядро фактически разполага с голяма част, ако не и пълното количество, от изчислителните ресурси налични в ядрото (модула, за предпочитащите официалната терминология) на Bulldozer. Поради това, избързвайки напред, производителност на Ivy Bridge базираните процесори не само не остъпва на тази на Bulldozer базираните, но дори ги и превъзхожда доста съществено.

Прехвърляйки се към конкретната имплементация, ядрото на Ivy Bridge разполага с 4 декодера на инструкции, подобно на Bulldozer, но за разлика от него те не са симетрични, като 3 от тях са по-упростени и могат да декодират една x86 инструкция в максимум една слята микрооперация – комбинация от една вътрешна за процесорното ядро инструкция за работа с паметта и аритметична операция или в единична микрооперация. За щастие огромната част от от инструкциите могат да се обработят именно по този начин. Последният декодер е по-скложен, като може да обработва и инструкции, които се декодират в до 4 слети микрооперации, в добавка на простите, на които са способни и останалите 3 блока. Останалите инструкции, чийто резултат е повече 4 микрооперации, се декодират от вътрешен микрокод, който може да изпрати до 4 микрооперации на такт към приемащата ги след декодерите декодерната опашка (Decode Queue).

Заедно с това декодерите са подкрепени от едно уникално за Intel решение, а именно микрокод кеш, който може да съхранява приблизително 1500 вече декодирани микрооперации и игре ролята на L0 инструкционен кеш с обем приблизително 6-8 КБ и използва 8-кратна асоциативност. Голямото му предимство, е че при повтаряне на кода на вече обработена х86 инструкция, то тя не се декоидра отново, а се използват данните от кеша и декодерите да се изключат, което помага доста от за енергоефективността на процесора. Заедно с това от микрокод кеша операциите се извличат на блокове от 32 байта, докато от L1 инструкционния кеш се извличат на двойно по-малки блокове – 16 байта, така че това е от сериозна полза и за производителността на процесора. Микрокодовия кеш дебютира в Pentium 4 архитектурата, като там играеше ролята изцяло на L1 инструкционен кеш, като в последствие в първите Core процесори компанията се отказа от неговото използване, но ето че в Sandy Bridge поколението се завърна към него.

Връщайки се малко назад, L1 инструкционния кеш на процесора е с размер 32 KB и има 8-кратна асоциативност, като информацията в него се зарежда и с помощта на вградени доста агресивни блокове за предварително извличане на данни от паметта. Инструкциите преминават и през блок за предсказване на разклоненията, който е от особена важност в съвремнните архитектури, като Intel не разкрива подробности за организацията му, но с голяма доза сигурност може ад се каже че ефективността му е по-висока от този използван в процесорите на AMD, като най-вероятно надвишва 95% точност. От кеша за инструкциите се извличат, както казахме, на блокове от 16 Б, като влизат в буфер за предварително декодиране от който могат да се подадат до 6 инструкции на такт към една от двете опашки с размер от 20 инструкции – по една за всеки от двата поддържани инструкционни потока на процесора. В последствие декодерите могат да извличат инструкции от двете опашки, като могат да сменят опашката на всеки такт.

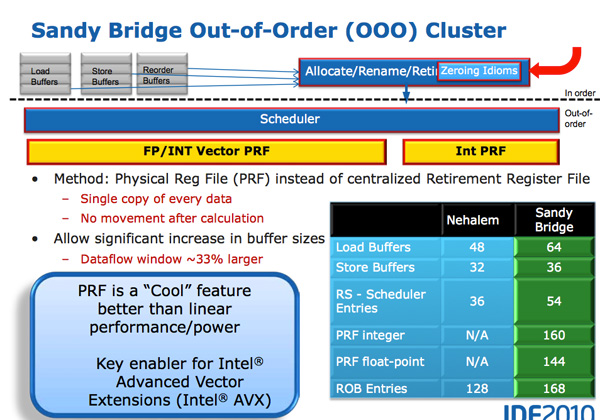

След декодирането микрооперациите попадат в декодерната опашка с размер 56 микрооперации. Това е и първата по-сериозна разлика между Sandy Bridge и Ivy Bridge архитектурите – в по-старата се използваха две опашки по 28 микрооперации. При работа с 2 нишки новата, по-голяма опашка се разделя статично по равно между двете, давайки отново по 28 микрооперации на нишка, но при работа с една нишка може да се използва целия размер от 56 микрооперации, което естествено води до известно повишение на еднонишковата производителност. След нея микрооперациите попадат в буфер за пренареждане (Reorder Buffer) с размер 168 микрооперации, където всъщност се случва основната част от непоредната обработка, като се следи последващото изпълнение на инструкциите и приключването им да става в правилния ред, както и се свързват архитектурните регистри на х86 инструкциите към физическия регистров файл на чипа. В * Bridge архитектурите Intel първи въведоха използването на физически регистров файл, като при изпълнението на операциите се предва указател към съответния регистър без да се прехвърлят данните от него, което е изключително енергоемка операция. Регистровия файл на Ivy Bridge разполага със 160 целочислени и 144 AVX/SSE/FP регистъра, буфер за разклонения с 48 елемента, буфер за зареждане на данни с 64 елемента и буфер за запис с 36 елемента. Може би тук е мястото да споменем, че AVX регистрите са 256-битови и за разлика от Bulldozer архитектурата на AMD една 256-битова AVX инструкция се декодира в една 256-битова вътрешна операция, а не в две 128-битови, което повишава ефективността на изпълнението. Това е свързано с вида на AVX блоковете в чипа, но до това ще стигнем малко по-късно.

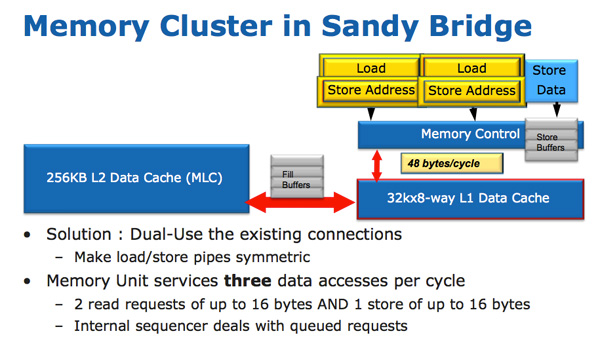

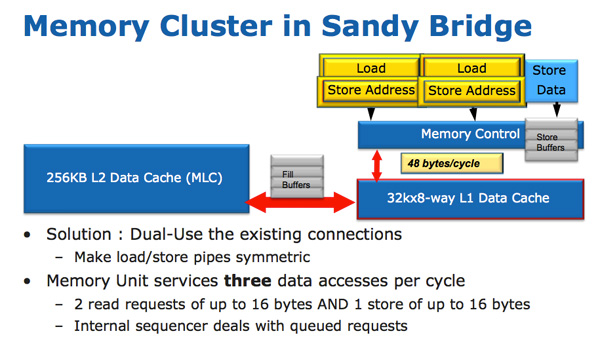

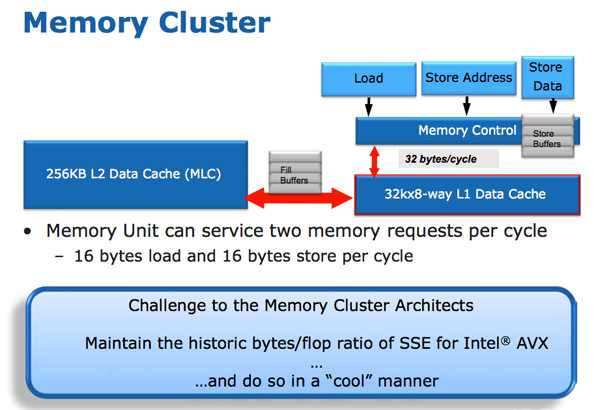

След буфера за пренареждане микрооперацитие попадат в унифициран диспечер, който може да поддържа до 54 операции в процес на изпълнение и е общ за целочислените и блоковете с плаваща запетая. В него слетите микрооперации се разбиват на отделните си елементи, като след това се предават на някой от 6-те изпълнителни порта на чипа. 3 от тях са запазени изключително за операции с паметта, като към тях са свързани поотделно две 64-битови устройства за генерация на адреси и един блок за запис в паметта. По този начин чипът може едновременно да извлече две стойности от паметта и да запише една, което на практика задоволява повечето операции. Заедно с това се използва и Memory Disabiguation технологията, която позволява спекулативно зареждане на данни преди завършването на операция за запис. Ползата от тази технология е доста висока, и позволява сериозно да се подобри производителността на работа с паметта.

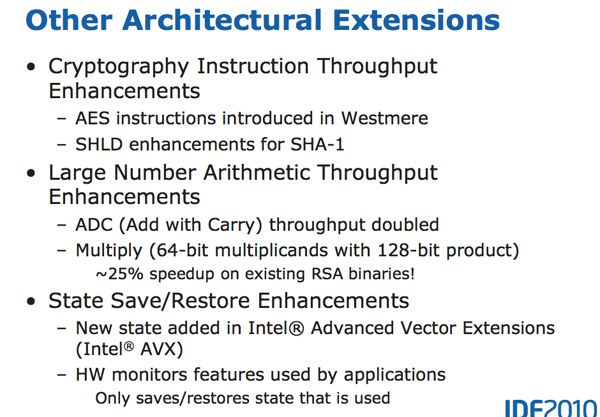

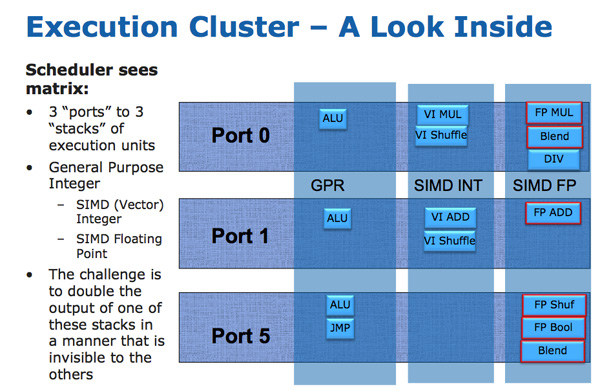

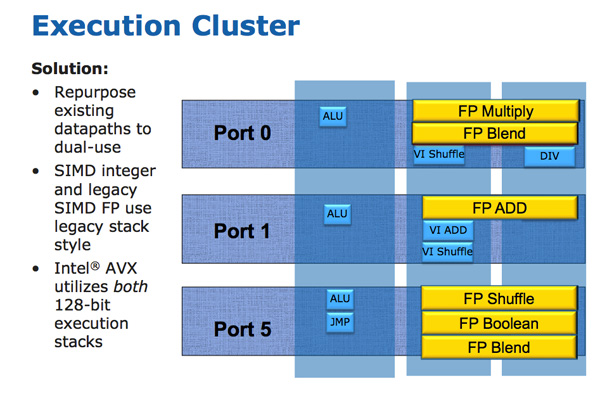

Останалите 3 порта пък са свързани с реалните аритметични устройва. С въвеждането на AVX, блоковете за изпълнение на операции с плаваща запетая се е наложило да се разширят до 256 бита. По принцип това би трябвало да означава и разширяване на съответстващите шини за данни до същата ширина и т.н., но на този етап AVX инструкциите не са особено често използвани и това би довело до голям разход на транзситори. За това инженерите на Intel са измислили един интересен трик, който да намали преразхода на транзистори – при работа на AVX устройства, те могат да използват част от шината за данни на целочислените векторни модули. Естествено, това означава че едновременото изпълнение на целочислени SIMD инструкции и AVX е невъзможно, което при смесени инструкции би довело до по-неефективна работа на програмата, но на този етап това е доста рядко срещана ситуация, така че този компромис е напълно в реда на нещата. Към трите изпълнителни порта са включени следните устройства – към първия порт са закачени целочислен скаларен АЛУ, който може да изпълнява и побитови операции, целочислен векторен умножител с възможност и за побитово преместване, умножител с плаваща запетая за изпълнение с възможност за изпълнение на смесване и блок за деление. Към втория порт са отново целочислен скаларен АЛУ, но с възможност за изпълнение на умножение, векторен целочислен блок, изпълняващ събиране и побитови операции и векторен блок с плаваща запетая за изпълнение на събиране. Към последният порт са закачени скаларен целочислен АЛУ с възможност за обработка на разклонения и векторен блок за плаваща запетая с възможност за изпълнение на побитови, логически и смесващи операции. Последните най-вероятно всъщност са групирани в един общ блок, наследник на по-знатия от старите архитектури FMisc или блок за специални операции. Отново да повторим – всички векторни блокове за плаваща запетая са с ширина 256-бита, за да поддръжат работата с AVX, но на тях се изпълняват също и различните 128-битови SSE инструкции, както и остатъчния х87 скаларен код.

В сравнение с Bulldozer, Ivy Bridge архитектурата разполага в рамките на ядрото си с 3 целочислени скаларни блока, 3 блока за работа с паметта (АГУ – адрес-генериращи устройства) и 3 блока за обработка на векторни операции с плаваща запетая. При това последните 3 са 256-битови и могат да работят едновременно, макар и не заедно с целочислените векторни блокове. За сравнение ядрото (модула) в Bulldozer има цели 4 скаларни целочислени АЛУ и 4 АГЛУ (АГУ с възможност за изпълнение на някои прости логически/аритметически операции) блока, но те са статично разделени в двойка клъстери, така че в това отношение Ivy Bridge би трябвало да има сериозно предимство при работа с една нишка, докато в добре оптмизирания многонишков целочислен код Bulldozer би трябвало да е с предимство. В същото време Bulldozer разполага с двойка 128-битови FMA блокове с плаваща запетая, които изпълняват и AVX/SSE/x87 инструкциите, както и с два блока за целочислени векторни операции. Тук сравнението е малко по-неясно, тъй като от една страна при нормален SSE/MMX/x87 код двата процесора имат теоретично еднаква производителност, но при AVX операциите и смесения код, нещата са трудно сравними. От една страна разбиването на 256-битовите AVX операции на две 128-битови намалява ефективността н а ООО частта на Bulldozer, както и намалява на половина производителността му при смесен AVX код (събиране+ умножение или друга операция). За сметка на това Ivy Bridge би имал много висока производителност при работа със смесен 256-битов AVX код, като може да изпълнява до 3 операции на такт, спрямо 1 от Bulldozer. В същото време обаче Bulldozer може едновременно да обработва и векторен целочислен код, заедно с AVX, както и използването на FMA би му позволило да извършва две операции едновременно (събиране + умножение) и има потенциал да изведе процесора поне на сходно ниво с Ivy Bridge в някои определени ситуации. Другата особеност на Bulldozer е, както видяхме, че поради специфичната му архитектура, една нишка не е способна ефективно да натовари целия векторен блок на процесора и отново в приложенията работещи с малко нишки Ivy Bridge би имал сериозно предимство. Като цяло може да се каже че макар блока на Bulldozer да е по-гъвкав, то работата с плаваща запетая при Ivy Bridge би трябвало да дава по-добра производителност в повечето типични сценарии.