Паралелна обработка на геометрията

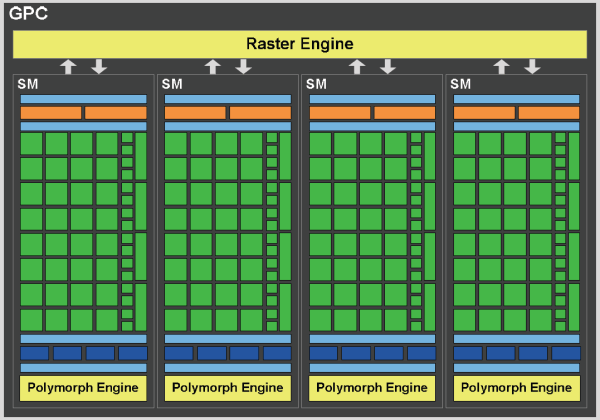

Клъстерът за графична обработка разполага със собствен растеризиращ блок и сетъп еднжин.

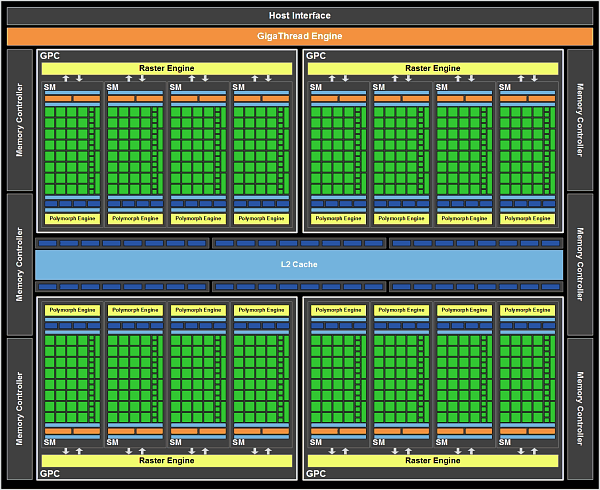

Клъстерът за графична обработка разполага със собствен растеризиращ блок и сетъп еднжин.И сега стигаме до революционното подобрение в чипа. 4 ПМ са групирани в един клъстер за графична обработка (КГО), като всеки клъстер се състои не само от тях, но включва и пълноценен растеризиращ блок занимаващ се с предварителната подготовка на полигоните, растери зидането и изрязването на невидимите повърхнини. Първата GF100 разполага общо с 4 такива клъстера или 16 ПМ. Това е първият графичен чип, който представя възможности за паралелна обработка на геометрията, като до този момент винаги този стадий е бил реализиран в един сериен блок. Частични стъпки в тази посока направи и ATI в Cypress, който разполага с два отделни растеризиращи блока, но сетъп енджина остава само един. Всеки геометричен блок има пикова производителност от 1 полигон на такт, от който могат да се растеризират 8 фрагмента на такт. Още по важна е тази промяна на фона на възможностите на GT200, чиято пикова производителност е 0,5 полигона на такт. Според Nvidia при все това реалните пикови възможности достигат до 3,2 полигона на такт, предвид някои вътрешни ограничения на чипа, което все пак е близо 7 пъти повече от предходното поколение и 3 пъти повече от конкурентните решения.

GF100 е съставен от 4 КГО и представлява нещо подобно на 4-ядрен процесор.

GF100 е съставен от 4 КГО и представлява нещо подобно на 4-ядрен процесор.Една от важните причини за тази промяна е вкарването на теселацията в конвейера на DirectX, при което е възможно от един полигон да се генерира допълнителна геометрия, която да е с 1-2 порядъка повече (максимум 64 пъти по спецификация), както и ефективно да се изпълняват някои техники за преобразуване на обектите, като дисплейсмънт мапинг. Цялото това количество може да доведе до задръстване на предишния единичен, последователен растеризиращ блок. Нещо повече, вече споменах че всеки ПМ разполага със собствен Polymorph Engine, който се грижи за подготовката на полигоните, теселирането , трансформацията, установяването на атрибутите и поточния изход, което предполага наистина сериозна геометрична мощ. По всичко личи че NVidia правят голям залог, че бъдещите игри ще използват много активно теселацията и ще се налага да обработват десетки пъти повече полигони.

Нова архитектура на паметта

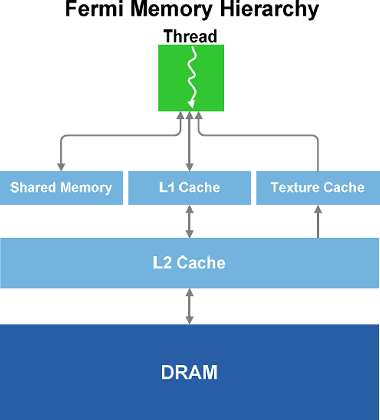

Според слуховете, Fermi e разработвана в началото като ултимативен изчислителен чип от Nvidia, конкурент на Larrabee на Intel, но провала на други разработки за върхов графичен чип налагат спешното комплектоване на чипа с някои типични графични блокове и скоростното му превръщане в графичен чип. Заедно с това DX11 също залага много сериозно на GPGPU изчисленията. Така че едва ли е учудващо, че освен вкарването на типичен L1 кеш в ПМ, Nvidia са преминали и към реализацията на пълноценен L2 кеш в чипа, който да служи за синхронизиране на данните между отделните блокове, както и за по-ефективна работа с нерегулярните алгоритми типични за изчислителните задачи. Не че предишните чипове нямаха също L2 кеш памет, но тя обикновено беше поделена между блоковете за растерни операции и беше възможно само да чете от нея. Във Fermi тя вече е обща и има пълноценни възможности за запис на данни. Обемът й е 768 КБ и е унифицирана за всички алгоритми и задачи, макар че на ниво ПМ все още има разделение между паметта за АЛУ и за текстуриращите модули.

След L2, единственото което остава, е локалната памет на графичния адаптер. Във Fermi това става през шест 64-битови контролера, всеки от които е обвързан с един блок РОП, който може да извършва блендинг и запис на 8 пиксела на такт и може да обработва 32 Z/stеncil отчета. Тук има известно презапасяване от страна на Nvidia, като очевидно чипът може да обработва максимум 32 фрагмента/пиксел на такт, но пък разполага с възможност да записва 48 такива в паметта. Това би било от полза при използване на антиалайзинг, който увеличава няколкократно броя на отчетите, които е нужно да се обработят за всеки пиксел. Заедно с това от Nvidia са подобрили и алгоритъма за Coverage Sampling Antialiasing, като вече е възможно да се използва 32x CSAA режим и CSAA да се прилага и за изглаждане на прозрачни текстури. Да ви припомня CSAA e начин за по-добро изчисляване на покритието на пиксела, като при това обаче не се използват повече текстурни семпли в сравнение с обичайните режими на AA, а просто се преизчислява по-точно цвета на пиксела на база на покритите полигони. Респективно от NVidia твърдят, че по този начин ефективно се получава качеството на по-висок режим на AA с минимална загуба на производителност. Според тестове, които съм правил преди това не е напълно вярно – наистина 8хCSAA например подобрява качеството спрямо нормалния 4xAA мултисемплинг, но качеството не е еквивалентно на 8хАА. Загубата на производителност обаче наистина е много малка. Новия режим и възможността за изглаждане на прозрачни текстури обаче би трябвало да подобрят още качеството. За съжаление за разлика от моделите на ATI няма официална поддръжка на суперсемплиране, макар че от няколко поколения адаптери съществуват начини за изкуственото прилагане на този режим. Суперсемплирането обаче може да се прилага локално, при използване на Transparency AA за изглаждане на прозрачни текстури.

Новата архитектура разполага с унифицирана, пълноценна L2 кеш памет

Новата архитектура разполага с унифицирана, пълноценна L2 кеш паметСпрямо предишното поколение контролерите и респективно шината на паметта са намалели от 8 канала/512-бита до 6 канала/384-бита, но пък се е появила най-накрая поддръжката на GDDR5 памет, която предлага над два пъти по-голяма пропускателна способност спрямо GDDR3 паметта. Потенциално това трябва да доведе до по-висока пропускателна способност спрямо GT200, въпреки по-тясната шина. Работата с този тип памет обаче е нещо доста ново все още за Nvidia, която до момента разполага цифром и словом само с един чип от нисък клас, в който да се прилага технологията – GT240. На свой ред той се появи доста скоро, така че опитът от него не е успял да помогне особено за Fermi. Самите инженери на NVidia признават, че не са разчели правилно някои от енергийните характеристики на контролерите на паметта. Това за съжаление е довело до проблеми с използването на високочестотните GDDR5 памети налични в момента, като максималните скорости на трансфер при Ферми са доста под 4000 МТ/с, докато конкурентите от ATI, които ползват такава памет вече 2 години за доста от чиповете си, постигат почти 5000 MT/с. Само тази разлика в честотите способна почти напълно да компенсира по-широката шина на Fermi. Предвид изчислителната насоченост на чипа, контролерите поддържат ECC корекция на грешки, но при това самите те не разполагат с допълнителните изводи, чрез които обикновено се реализира тази поддръжка (64-битов канал с поддръжка на ECC би трябвало да използва 72-битова шина). Това се реализира като част от паметта на картите се резервира за съхраняване на допълнителните данни за проверка по четност, като предаването им се разхвърля по всички канали на паметта. При това положение обаче според Nvidia ефективната загуба на пропускателна способност е по-малка от очакваните 12,5%, поради някои специални настройки, които са направили. Така или иначе за повечето от вас това не е важно, тъй като ECC корекция на грешки ще бъде използвана само при професионалните изчислителни адаптери от серията Tesla.

No comments yet.