Преди около 3 години изглеждаше, че Intel прави революция – за пръв път компанията създаде съзнателно бавен процесор. Това беше Atom и идеята му беше да предостави максимално евтина и енергийно ефективна платформа. Голямата цел, разбира се, беше влизането при мобилните телефони, където оборотите в наши дни са с пъти, ако не и с десетки пъти по-големи, отколкото при компютрите. За Atom целта още беше далечна, но Intel явно беше решила да се възползва от евентуалните възможности, предлагани от новото ядро. И така внезапно изникна пазара на нетбук компютри, създадени за да оползотворят новия процесор.

Изглежда обаче Intel фатално подцени конкурентите си от лагера на ARМ съвместимите процесори, които в момента царуват на пазара за смартфони. А те изобщо не смятат да предават позициите само защото на една гигантска компания нещо и се върти из главата. През изминалите години ARM базираните процесори и системи-в-чип (СВЦ) увеличиха производителността си в пъти, като в същото време запазиха и дори подобриха консумацията си. С Atom обаче Intel допусна поредица от грешки. На първо място комплектовката с чипсети в началото на предлагането на процесора беше меко казано малоумна – какъв е смисъла да предлагаш 2,5-ватов процесор с 5-ватов чипсет? Или още повече на 4-ватов процесор и 22-ватов чипсет, каквато беше неттоп версията на Атом. И то с драстично остаряло графично ядро. Заедно с това компанията не се възползва навреме да прехвърли процесорите към 32-нанометров процес и накрая подобренията в производителността на процесора бяха изцяло по екстензивен път чрез добавяне на още ядра и минималистичен ръст на тактовата честота. Благодарение на това ARM не просто скъси дистанция, а дори може да се каже, че настигна и дори изпревари в някои области Atom. Като при това консумацията от 1-2 вата остана. Консумацията на системи с Atom междувременно се снижи за сметка на интегрирането на почти целия чипсет заедно с ядрата, но остава в пъти по-голяма от тази на конкурентите. Не на последно място цената на платформата н Intel остава многократно по-висока.

Затова едва ли е учудващо, че на практика никой производител с малко акъл в главата не използва Аtom в прохождащите в момента таблети, а пазара на нетбуци достигна пика си и изглежда започва да спада, като и при него започна инвазията на ARM. По всичко изглежда, че новата ревизия на Atom е отчайващо нужна, а няма никакви изгледи да се появи преди лятото. А тогава ще трябва да се изправи срещу вече 4-ядрени ARM СВЧ. И за да е всичко максимално драматично, вечния конкурент на Intel, очакващ гиганта да допусне грешка, изглежда заби и последния нож в гърба на Atom, като анонсира собствена ултрамобилна платформа.

Bobcat…

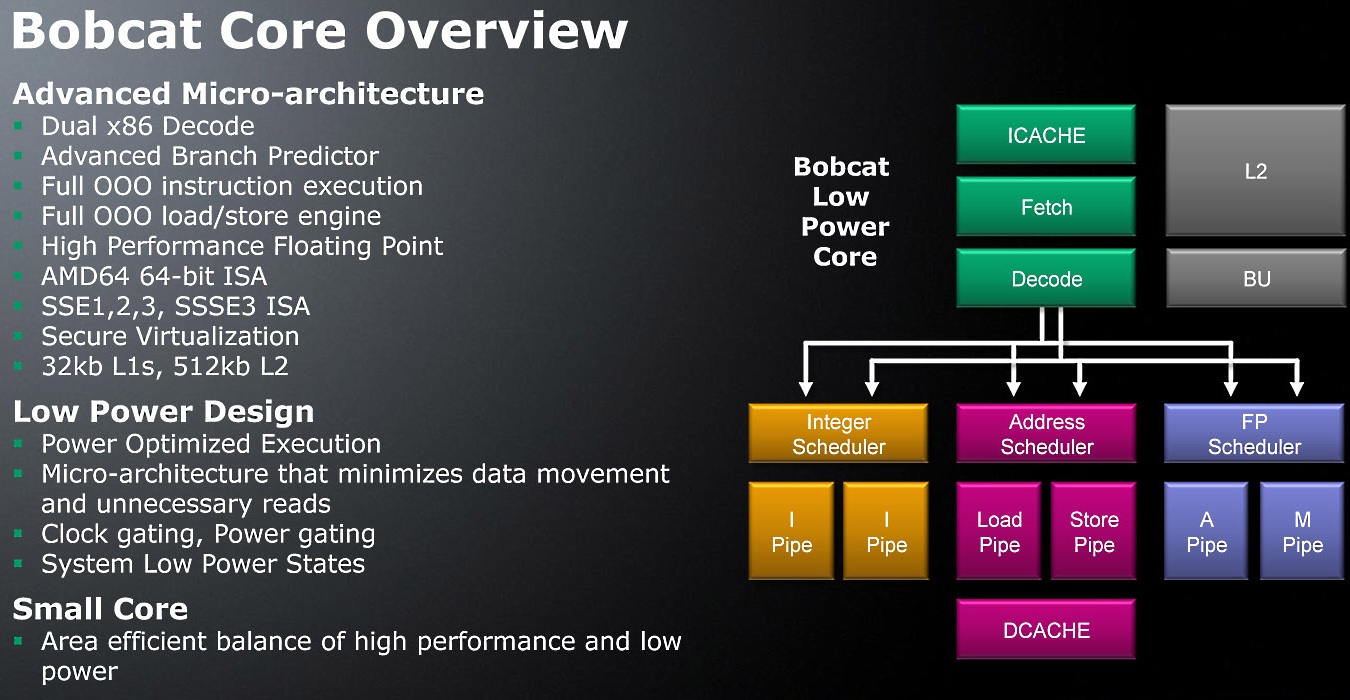

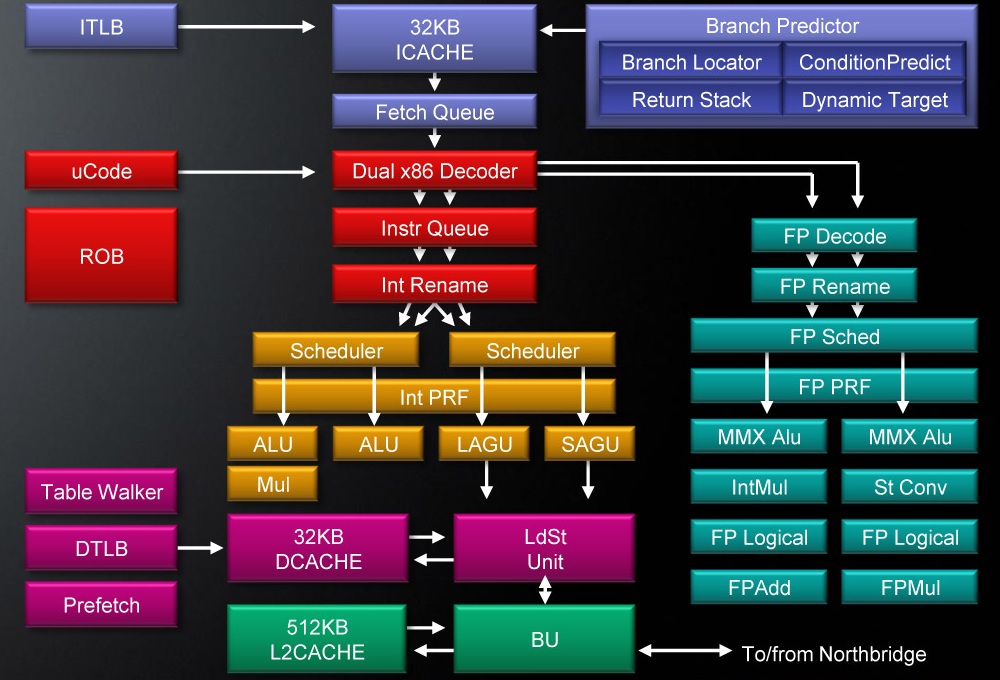

…e кодовото име на процесорното ядро използвано в новата платформа. Подобно на Atom, за да постигнат целите като консумация и производителност от AMD са разработили изцяло нова архитектура. Тя е 64-битова с непоредно изпълнение и с възможност за изпълнение на две инструкции на такт – доста по-модерна концепция в сравнение с Atom. Големият проблем на x86 архитектурите е декодирането на инструкциите във вътрешни операции за процесора (микрооперации), тъй като тези блокове реално не изпълняват полезна работа, а консумират енергия и то доста. За това и Intel, и AMD са избрали подхода с декодиране на две инструкции на такт, за разлика от моделите им от по-висок клас, разполагащи с по 3 и 4 декодера. В общия случай за този клас процесори допълнителните декодери водят до малък прираст в производителност. Според AMD компанията е успяла да настрои декодерите така, че 89% от x86 инструкциите да се декодират в единична микрооперация, 10% се декодират в две слети микрооперации и останалите около 1% се декодират чрез микрокод в повече от 2 инструкции.

Изчислителното ядро е балансирано спрямо двата декодера, като разполага с два конвейера, всеки от които е от двойка АЛУ и УГА. Устройствата са свързани към два отделни диспечера, като единия може да подава по две операции на такт към АЛУ, едно от които може да изпълнява и умножение, а втория се грижи за двете устройства за генерация на адреси, които са съответно за зарежда от паметта и запис в нея. За операциите с плаваща запетая се грижи отделен диспечер, отново с възможност за по даване на две операции на такт, като има два модула за работа с плаваща запетая и SSE/MMX инструкции, които се обработват съответно събирането и умножението. Устройството за събиране изпълнява и ролята на целочислен множител. Поддържаните разширения са всички до SSE4A, като единствено най-новите AXP и XOP, появили се в SandyBridge не могат да се използват. Така или иначе за профила на използване на Bobcat това не е особен проблем. Слабата черта обаче е, че двата модула за работа с плаваща запетая са 64-битови, докато Atom и другият х86 конкурент в свръхмобилния клас – VIA Nano използват 128-битови блокове и потенциално имат много по-висока производителност в такива операции. Изглежда от AMD са изтъргували непоредното изпълнение на инструкциите за сметка на намалената FP производителност. Това в известна степен е логично, тъй като според концепцията на компанията за интензивна работа с плаваща запетая се предполага да се използват шейдерите на интегрираното графично ядро. За това обаче още доста оптимизиране на софтуера.

За съжаление не разполагам с данни колко голям е инструкционният прозорец за непоредното изпълнение, но предвид насочеността на чипа бих предположил, че е значително по-малък от тази на актуалните модели от висок клас на фирмите, може би от порядъка на 24-48 инструкции. Заедно с това чипът използва и модерен блок за предсказване на разклоненията, но отново няма подробности как точно е реализиран. Конвейера на чипа е 15-стъпков с 13 такта „наказание“ за грешно предсказване на преходите, така че би трябвало да се използва блок със сравнително висока точност, но със сигурност няма да е на нивото на по-високия клас процесори. Кеш паметта от първо ниво е по 32 КБ за инструкции и данни, с 8-кратна асоциативност и 3 тактова латентност, а L2 кеша е 512КБ с 16-кратна асоциативност и 17 тактова латентност и е индивидуална за всяко ядро.